Solucionar problemas da mensagem "QM_SANITY_WARNING" no roteador 12000 Series

Opções de download

Linguagem imparcial

O conjunto de documentação deste produto faz o possível para usar uma linguagem imparcial. Para os fins deste conjunto de documentação, a imparcialidade é definida como uma linguagem que não implica em discriminação baseada em idade, deficiência, gênero, identidade racial, identidade étnica, orientação sexual, status socioeconômico e interseccionalidade. Pode haver exceções na documentação devido à linguagem codificada nas interfaces de usuário do software do produto, linguagem usada com base na documentação de RFP ou linguagem usada por um produto de terceiros referenciado. Saiba mais sobre como a Cisco está usando a linguagem inclusiva.

Sobre esta tradução

A Cisco traduziu este documento com a ajuda de tecnologias de tradução automática e humana para oferecer conteúdo de suporte aos seus usuários no seu próprio idioma, independentemente da localização. Observe que mesmo a melhor tradução automática não será tão precisa quanto as realizadas por um tradutor profissional. A Cisco Systems, Inc. não se responsabiliza pela precisão destas traduções e recomenda que o documento original em inglês (link fornecido) seja sempre consultado.

Introdução

Este documento descreve o procedimento para depurar mensagens de esgotamento de buffer de pacote que podem ocorrer em diferentes placas de linha em um roteador Cisco da série 12000 que esteja executando o IOS. É muito comum ver o tempo e os recursos valiosos desperdiçados substituindo o hardware que realmente funciona corretamente devido à falta de conhecimento sobre o gerenciamento de buffer GSR.

Pré-requisitos

Requisitos

O leitor deve ter uma visão geral da arquitetura do Cisco 12000 Series Router.

Componentes Utilizados

As informações neste documento são baseadas nestas versões de software e hardware:

- Cisco 12000 Series Internet Router

- Versão do Cisco IOS® Software que suporta o Gigabit Switch Router

As informações neste documento foram criadas a partir de dispositivos em um ambiente de laboratório específico. Todos os dispositivos usados neste documento são iniciados com uma configuração limpa (padrão). Se a sua rede estiver ativa, certifique-se de que entende o impacto potencial de qualquer comando.

Conventions

Consulte as Convenções de Dicas Técnicas da Cisco para obter mais informações sobre convenções de documentos.

Problema

Os roteadores GSR ou 12000 Series da Cisco possuem uma arquitetura realmente distribuída. Isso significa que cada LC executa sua própria cópia da imagem do software Cisco IOS e tem a inteligência para concluir sozinho a decisão de encaminhamento de pacotes. Cada placa de linha faz seu próprio

- Pesquisa de encaminhamento

- Gerenciamento de buffer de pacote

- QOS

- Controle de fluxo

Uma das operações mais importantes durante a comutação de pacotes no GSR é o gerenciamento de buffer que é feito por vários ASICs de Gerenciamento de Buffer ( BMA) localizados nas placas de linha. Abaixo estão algumas mensagens relacionadas ao gerenciamento de buffer GSR que podem aparecer nos logs do roteador durante a produção. Na seção a seguir, discutiremos os diferentes disparadores que poderiam fazer com que essas mensagens aparecessem nos registros do roteador e quais são as ações corretivas a serem feitas para mitigar o problema. Em algumas situações, isso também pode levar à perda de pacotes, que pode se manifestar como oscilações de protocolo e causar impacto na rede.

%EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted

SLOT 1:Sep 16 19:06:40.003 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(1) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:45.943 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(0) are available in ToFab FreeQ pool# 1

SLOT 0:Sep 16 19:06:46.267 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(2) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:47.455 UTC: %EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted. Recarving the ToFab buffers

SLOT 8:Sep 16 19:06:47.471 UTC: %EE192-3-BM_QUIESCE:

Solução

Background

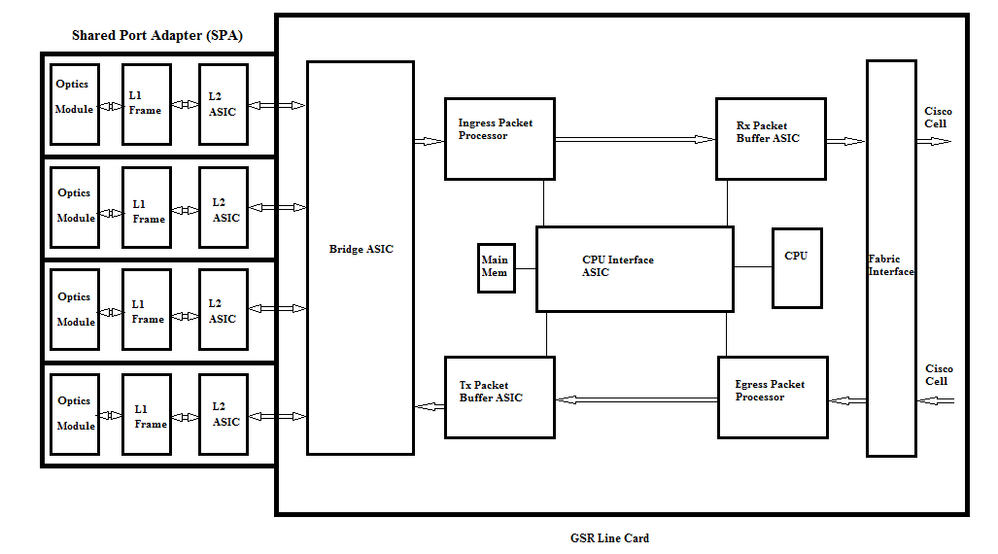

Para solucionar os erros de aviso do QM-SANITY, precisamos entender o fluxo de pacotes em uma placa de linha GSR. A figura abaixo explica os blocos principais de uma placa de linha C12k e o caminho do fluxo de pacotes.

A Placa de Linha (LC) em um Cisco 12000 Series Internet Router tem dois tipos de memória:

- Memória de roteamento ou processador (RAM dinâmica - DRAM): essa memória permite principalmente que o processador integrado execute o software Cisco IOS e armazene tabelas de roteamento de rede (Base de informações de encaminhamento - FIB, adjacência)

- Memória de pacote (Synchronous Dynamic RAM - SDRAM): a memória de pacote da placa de linha armazena temporariamente os pacotes de dados aguardando decisões de comutação pelo processador da placa de linha.

Como visto na imagem acima, a placa de linha GSR tem um buffer de pacote especializado ASIC (Application Specific Integrated Circuit), um em cada direção do fluxo de tráfego que fornece acesso à memória do pacote.Esses ASICs também conhecidos como ASIC de gerenciamento de buffer ( BMA) fazem a bufferização de pacote e a função de gerenciamento de fila de buffer na placa de linha. Para suportar altas taxas de transferência/encaminhamento, a memória do pacote em qualquer direção é gravada em pools de memória de tamanhos diferentes projetados para encaminhar pacotes de tamanhos de MTU variados.

Os quadros recebidos pelas placas do Módulo de Interface de Camada Física (PLIM - Physical Layer Interface Module) são processados na Camada 2 e DMAed para uma memória local na placa PLIM. Quando a unidade de dados recebida estiver completa, um ASIC no PLIM entra em contato com o BMA de entrada e solicita um buffer de tamanho apropriado. Se o buffer for concedido, o pacote será movido para a memória do pacote de entrada da placa de linha. Se não houver buffers disponíveis, o pacote será descartado e o contador de interface ignorado será ativado. O processador de pacotes de entrada executa o processamento de recursos no pacote, toma a decisão de encaminhamento e move o pacote para a fila toFab correspondente à placa de linha de saída. O ASIC da interface de estrutura (FIA) segmenta o pacote para as células cisco e a célula é transmitida para a matriz de comutação. Os pacotes são recebidos da matriz de comutação pelo FIA na placa de linha de saída e vão para as filas Frfab onde são reagrupados, depois para o PLIM de saída e, finalmente, enviados no fio.

A decisão do BMA FrFab de selecionar o buffer de um conjunto de buffers específico é baseada na decisão tomada pelo mecanismo de switching da placa de linha de entrada. Como todas as filas da caixa inteira são do mesmo tamanho e na mesma ordem, o mecanismo de switching informa ao LC transmissor para colocar o pacote na mesma fila numérica a partir da qual ele entrou no roteador.

Enquanto o pacote está sendo comutado, o tamanho da fila de um conjunto de buffers específico na placa de linha de entrada que foi usada para mover o pacote será diminuído em um até que o BMA na placa de linha de saída retorne o buffer. Aqui, também devemos observar que o gerenciamento completo de buffer é feito em hardware pelo ASIC de gerenciamento de buffer e, para uma operação sem falhas, é necessário que o BMA retorne os buffers para o pool original de onde ele foi originado.

Há três cenários em que o gerenciamento de buffer de pacote GSR pode sofrer estresse ou falha, levando à perda de pacotes. Abaixo estão os três cenários.

Cenário 1:

O gerenciamento da fila de hardware falha. Isso acontece quando o BMA de saída não retorna o buffer de pacote ou retorna o buffer de pacote para o pool de buffer incorreto. Se os buffers retornarem ao pool incorreto, veremos alguns pools de buffer crescendo e alguns pools de buffer esgotados ao longo de um período de tempo e, por fim, afetando pacotes com o tamanho do pool de buffer esgotado. Começaremos a ver os avisos de QM-Sanity quando o buffer de pacote esgotar e ultrapassar o limite de aviso.

Use o comando QM sanity debugs e show controllers tofab queues para verificar se você foi afetado por essa condição. Consulte a seção de Troubleshooting para descobrir como ativar os limiares de sanidade do QM.

Essa condição é geralmente causada por hardware defeituoso. Verifique as saídas abaixo no roteador e procure erros de paridade ou travamentos na placa de linha. A correção seria substituir a placa de linha.

show controllers fia

show context all

show log

Exemplo:

Nas depurações de sanidade do QM e na fila show controller tofab podemos ver que o Pool 2 está crescendo em tamanho enquanto o Pool 4 está baixo. Isso indica que o Pool 4 está perdendo buffers e está sendo retornado para o Pool 2.

Depurações de sanidade do QM:

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 1: Carve Size 102001: Current Size 73078

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 2: Carve Size 78462: Current Size 181569

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 3: Carve Size 57539: Current Size 6160

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 4: Carve Size 22870: Current Size 67

SLOT 5:Oct 25 04:41:03.286 UTC: IPC FreeQ: Carve Size 600: Current Size 600

show controllers tofab queues:

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 13542 13448 73078 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 131784 131833 181569 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 184620 182591 6160 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 239113 238805 67 262143

Cenário 2:

Congestionamento de tráfego no dispositivo do próximo salto ou no caminho de encaminhamento. Neste cenário, o dispositivo para o qual o GSR alimenta o tráfego não pode processar na velocidade do GSR e, como resultado, o dispositivo do próximo salto está enviando quadros de pausa em direção ao GSR solicitando que ele reduza a velocidade. Se o controle de fluxo estiver ativado nas placas GSR PLIM , o roteador respeitará os quadros de pausa e começará a armazenar os pacotes em buffer. Eventualmente, o roteador ficará sem buffers, causando as mensagens de erro de sanidade do QM e quedas de pacotes. Começaremos a ver os avisos de QM-Sanity quando o buffer de pacote esgotar e ultrapassar o limite de aviso. Consulte a seção de Troubleshooting para saber como encontrar os limiares de sanidade do QM.

Use a saída show interface na interface de saída para verificar se o roteador é afetado por esse cenário. A captura abaixo fornece um exemplo de uma interface que recebe quadros de pausa. O plano de ação será examinar a causa do congestionamento no dispositivo do próximo salto.

GigabitEthernet6/2 is up, line protocol is up

Small Factor Pluggable Optics okay

Hardware is GigMac 4 Port GigabitEthernet, address is 000b.455d.ee02 (bia 000b.455d.ee02)

Description: Cisco Sydney Lab

Internet address is 219.158.33.86/30

MTU 1500 bytes, BW 500000 Kbit, DLY 10 usec, rely 255/255, load 154/255

Encapsulation ARPA, loopback not set

Keepalive set (10 sec)

Full Duplex, 1000Mbps, link type is force-up, media type is LX

output flow-control is on, input flow-control is on

ARP type: ARPA, ARP Timeout 04:00:00

Last input 00:00:02, output 00:00:02, output hang never

Last clearing of "show interface" counters 7w1d

Queueing strategy: random early detection (WRED)

Output queue 0/40, 22713601 drops; input queue 0/75, 736369 drops

Available Bandwidth 224992 kilobits/sec

30 second input rate 309068000 bits/sec, 49414 packets/sec

30 second output rate 303400000 bits/sec, 73826 packets/sec

143009959974 packets input, 88976134206186 bytes, 0 no buffer

Received 7352 broadcasts, 0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored

0 watchdog, 7352 multicast, 45 pause input

234821393504 packets output, 119276570730993 bytes, 0 underruns

Transmitted 73201 broadcasts

0 output errors, 0 collisions, 0 interface resets

0 babbles, 0 late collision, 0 deferred

0 lost carrier, 0 no carrier, 0 pause output

0 output buffer failures, 0 output buffers swapped out

Cenário 3:

Em momentos de excesso de assinaturas devido a um projeto de rede ruim/picos de tráfego/ataque de DOS. O aviso de QM Sanity pode ocorrer se houver uma condição de tráfego alto e contínuo, em que mais tráfego é direcionado ao roteador do que o que as placas de linha podem suportar.

Para fazer isso, verifique as taxas de tráfego em todas as interfaces no roteador. Isso revelará se algum dos links de alta velocidade está congestionando links lentos.

Use o comando show interface output.

Comandos de solução de problemas

Para verificar o nível de sanidade do QM atual para um LC

-

Anexar ao LC

-

Vá para o modo enable

-

Executar o comando test fab

-

Colete a saída de "qm_sanity_info"

-

Opção q para sair da linha de comando test fab

-

Sair do LC

Para configurar os parâmetros de sanidade do QM

- alterar para modo de configuração

- Execute hw-module slot <slot#> qm-sanity tofab warning freq <>

Para ativar/desativar depurações de sanidade do QM

- Anexar ao LC

-

Vá para o modo enable

-

Executar o comando test fab

-

Execute "qm_sanity_debug". Executar novamente e as depurações serão interrompidas

-

Opção q para sair da linha de comando test fab

-

Sair do LC

Para verificar as estatísticas básicas da interface de estrutura GSR

- show controller fia

Para verificar as filas Tofab

- show controllers tofab queues

Para verificar as filas Frfab

- show controller frfab queues

Exemplo:

A saída abaixo é retirada de um roteador de laboratório em funcionamento para demonstrar as saídas do comando.

GSR-1-PE-5#show controller fia

Fabric configuration: 10Gbps bandwidth (2.4Gbps available), redundant fabric

Master Scheduler: Slot 17 Backup Scheduler: Slot 16

Fab epoch no 0 Halt count 0

From Fabric FIA Errors

-----------------------

redund overflow 0 cell drops 0

cell parity 0

Switch cards present 0x001F Slots 16 17 18 19 20

Switch cards monitored 0x001F Slots 16 17 18 19 20

Slot: 16 17 18 19 20

Name: csc0 csc1 sfc0 sfc1 sfc2

-------- -------- -------- -------- --------

los 0 0 0 0 0

state Off Off Off Off Off

crc16 0 0 0 0 0

To Fabric FIA Errors

-----------------------

sca not pres 0 req error 0 uni fifo overflow 0

grant parity 0 multi req 0 uni fifo undrflow 0

cntrl parity 0 uni req 0

multi fifo 0 empty dst req 0 handshake error 0

cell parity 0

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_debug

QM Sanity Debug enabled

BFLC (? for help) [qm_sanity_debug]:

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

QM Sanity Debug disabled

BFLC (? for help) [qm_sanity_debug]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 20 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exi

Disconnecting from slot 1.

Connection Duration: 00:01:09

GSR-1-PE-5#config t

Enter configuration commands, one per line. End with CNTL/Z.

GSR-1-PE-5(config)#hw-module slot 1 qm-sanity tofab warning freq 10

GSR-1-PE-5(config)#end

GSR-1-PE-5#attach 1

02:57:25: %SYS-5-CONFIG_I: Configured from console by console

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 10 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exit

Disconnecting from slot 1.

Connection Duration: 00:00:27

GSR-1-PE-5#execute-on all show controllers tofab queues

========= Line Card (Slot 0) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262141/262141 buffers specified/carved

265028848/265028848 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

107232/107232 (buffers specified/carved), 40.90%, 80 byte data size

601 107832 107232 262143

73232/73232 (buffers specified/carved), 27.93%, 608 byte data size

107833 181064 73232 262143

57539/57539 (buffers specified/carved), 21.94%, 1616 byte data size

181065 238603 57539 262143

23538/23538 (buffers specified/carved), 8.97%, 4592 byte data size

238604 262141 23538 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

155 154 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

15 2191(hpr) 0 0 0 0

Multicast 2048 0 0 0 262143

2049 0 0 0 262143

========= Line Card (Slot 1) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: 26000000, carve base: 26010000

268369920 bytes carve size, 4 SDRAM bank(s), 32768 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262140/261472 buffers specified/carved

267790176/264701344 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 601 102601 102001 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 102602 181063 78462 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 181064 238602 57539 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 238603 261472 22870 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

30 85 84 600 262143

Raw Queue (high priority):

27 0 0 0 65368

Raw Queue (medium priority):

28 0 0 0 32684

Raw Queue (low priority):

31 0 0 0 16342

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

=============================================================

::::::::::::::::::::

Hi Priority

0 2176(hpr) 0 0 0

1 2177(hpr) 0 0 0

2 2178(hpr) 0 0 0

3 2179(hpr) 0 0 0

4 2180(hpr) 553 552 0

5 2181(hpr) 0 0 0

6 2182(hpr) 0 0 0

7 2183(hpr) 0 0 0

8 2184(hpr) 0 0 0

9 2185(hpr) 0 0 0

10 2186(hpr) 0 0 0

11 2187(hpr) 0 0 0

12 2188(hpr) 0 0 0

13 2189(hpr) 0 0 0

14 2190(hpr) 0 0 0

15 2191(hpr) 0 0 0

Multicast

2048 0 0 0

2049 0 0 0

2050 0 0 0

2051 0 0 0

2052 0 0 0

2053 0 0 0

2054 0 0 0

2055 0 0 0

========= Line Card (Slot 3) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4112 bytes, min buffer data size 80 bytes

262142/262142 buffers specified/carved

230886224/230886224 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

3 non-IPC free queues:

94155/94155 (buffers specified/carved), 35.91%, 80 byte data size

601 94755 94155 262143

57539/57539 (buffers specified/carved), 21.94%, 608 byte data size

94756 152294 57539 262143

109848/109848 (buffers specified/carved), 41.90%, 1616 byte data size

152295 262142 109848 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

207 206 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

1 0 0 0 262143

2 0 0 0 262143

3 0 0 0 262143

:::::::::::::::::::::::::::

2049 0 0 0 262143

2050 0 0 0 262143

2051 0 0 0 262143

2052 0 0 0 262143

2053 0 0 0 262143

2054 0 0 0 262143

2055 0 0 0 262143

GSR-1-PE-5#execute-on slot 2 show controller frfab queues

========= Line Card (Slot 2) =========

Carve information for FrFab buffers

SDRAM size: 268435456 bytes, address: D0000000, carve base: D241D100

230567680 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

235926/235926 buffers specified/carved

226853664/226853664 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

96484/96484 (buffers specified/carved), 40.89%, 80 byte data size

11598 11597 96484 262143

77658/77658 (buffers specified/carved), 32.91%, 608 byte data size

103116 103115 77658 262143

40005/40005 (buffers specified/carved), 16.95%, 1616 byte data size

178588 178587 40005 262143

21179/21179 (buffers specified/carved), 8.97%, 4592 byte data size

214748 235926 21179 262143

IPC Queue:

600/600 (buffers specified/carved), 0.25%, 4112 byte data size

66 65 600 262143

Multicast Raw Queue:

0 0 0 58981

Multicast Replication Free Queue:

235930 262143 26214 262143

Raw Queue (high priority):

78 77 0 235927

Raw Queue (medium priority):

11596 11595 0 58981

Raw Queue (low priority):

0 0 0 23592

Interface Queues:

Interface Queue# Head Tail Length Threshold

pkts pkts

======================================================

0 0 103107 103106 0 32768

3 178588 178587 0 32768

1 4 103110 103109 0 32768

7 11586 11585 0 32768

2 8 0 0 0 32768

11 0 0 0 32768

3 12 0 0 0 32768

15 0 0 0 32768

GSR-1-PE-5#

Histórico de revisões

| Revisão | Data de publicação | Comentários |

|---|---|---|

1.0 |

30-Jul-2017 |

Versão inicial |

Colaborado por engenheiros da Cisco

- Shabeer MansoorTAC da Cisco

Contate a Cisco

- Abrir um caso de suporte

- (É necessário um Contrato de Serviço da Cisco)

Feedback

Feedback