BTB Interface Connector Overview

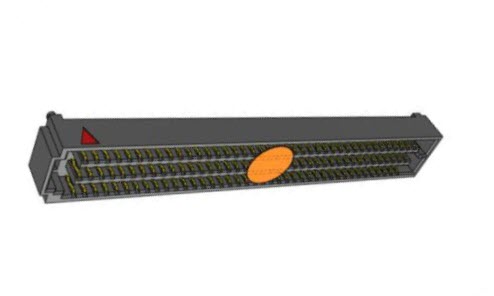

The board-to-board (BTB) connector provides the power input and the interface to external devices. This connector belongs to the SEARAY® Connector Series from SAMTEC. Depending on the mating connector selected by the integrator, the series supports a stacking height from 7mm to 18mm (not all increments are supported). The BTB connector on the ESR is the SAMTEC SEAF-40-05.0-S-06-2-A-K 240-pin female connector.

Complete information on the connector can be found at the Samtec website:

https://www.samtec.com/connectors/high-speed-board-to-board/high-density-arrays/searay

Note |

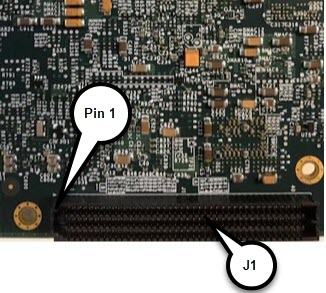

This figure is a partial view of the PCB to highlight the connector. |

The following table lists the mating connector (SEAM lead style) options that are available to achieve specific stacking heights when coupled with the ESR (-05.0 SEAF lead style).

|

Mating Connector SEAM Lead Style |

ESR Connector J1-05.0 SEAF Lead Style |

|---|---|

|

-02.0 |

7mm |

|

-03.0 |

8mm |

|

-03.5 |

8.5mm |

|

-05.5 |

N/A |

|

-06.5 |

11.5mm |

|

-07.0 |

12mm |

|

-09.0 |

14mm |

|

-11.0 |

16mm |

|

-13.0(not tooled) |

18mm |

Feedback

Feedback