Fehlerbehebung: "QM_SANITY_WARNING" Nachricht bei Router der Serie 12000

Download-Optionen

-

ePub (172.3 KB)

In verschiedenen Apps auf iPhone, iPad, Android, Sony Reader oder Windows Phone anzeigen

Inklusive Sprache

In dem Dokumentationssatz für dieses Produkt wird die Verwendung inklusiver Sprache angestrebt. Für die Zwecke dieses Dokumentationssatzes wird Sprache als „inklusiv“ verstanden, wenn sie keine Diskriminierung aufgrund von Alter, körperlicher und/oder geistiger Behinderung, Geschlechtszugehörigkeit und -identität, ethnischer Identität, sexueller Orientierung, sozioökonomischem Status und Intersektionalität impliziert. Dennoch können in der Dokumentation stilistische Abweichungen von diesem Bemühen auftreten, wenn Text verwendet wird, der in Benutzeroberflächen der Produktsoftware fest codiert ist, auf RFP-Dokumentation basiert oder von einem genannten Drittanbieterprodukt verwendet wird. Hier erfahren Sie mehr darüber, wie Cisco inklusive Sprache verwendet.

Informationen zu dieser Übersetzung

Cisco hat dieses Dokument maschinell übersetzen und von einem menschlichen Übersetzer editieren und korrigieren lassen, um unseren Benutzern auf der ganzen Welt Support-Inhalte in ihrer eigenen Sprache zu bieten. Bitte beachten Sie, dass selbst die beste maschinelle Übersetzung nicht so genau ist wie eine von einem professionellen Übersetzer angefertigte. Cisco Systems, Inc. übernimmt keine Haftung für die Richtigkeit dieser Übersetzungen und empfiehlt, immer das englische Originaldokument (siehe bereitgestellter Link) heranzuziehen.

Einleitung

In diesem Dokument wird das Verfahren zum Debuggen von Paketpuffer-Erschöpfungsmeldungen beschrieben, die auf verschiedenen Linecards in einem Cisco Router der Serie 12000 mit IOS auftreten können. Es kommt viel zu häufig vor, dass wertvolle Zeit und Ressourcen verschwendet werden, um die Hardware zu ersetzen, die aufgrund mangelnder Kenntnisse über das GSR-Puffermanagement tatsächlich ordnungsgemäß funktioniert.

Voraussetzungen

Anforderungen

Der Leser sollte einen Überblick über die Architektur der Cisco Router der Serie 12000 erhalten.

Verwendete Komponenten

Die Informationen in diesem Dokument basierend auf folgenden Software- und Hardware-Versionen:

- Cisco Internet Router der Serie 12000

- Cisco IOS® Softwareversion, die den Gigabit-Switch-Router unterstützt

Die Informationen in diesem Dokument beziehen sich auf Geräte in einer speziell eingerichteten Testumgebung. Alle in diesem Dokument verwendeten Geräte werden mit einer gelöschten (Standard-)Konfiguration gestartet. Wenn Ihr Netz Live ist, überprüfen Sie, ob Sie die mögliche Auswirkung jedes möglichen Befehls verstehen.

Konventionen

Weitere Informationen zu Dokumentkonventionen finden Sie unter Cisco Technical Tips Conventions (Technische Tipps von Cisco zu Konventionen).

Problem

Cisco Router der Serien GSR oder 12000 verfügen über eine vollständig verteilte Architektur. Das bedeutet, dass jeder LC seine eigene Kopie des Cisco IOS Software-Images ausführt und über die nötigen Informationen verfügt, um die Paketweiterleitungsentscheidung selbst zu treffen. Jede Linecard führt ihre eigenen Aktionen aus

- Weiterleitungs-Suche

- Paketpuffer-Management

- QoS

- Flusssteuerung

Eine der wichtigsten Operationen beim Paketvermitteln in GSR ist das Puffermanagement, das von verschiedenen Buffer Management ASICs (BMA) durchgeführt wird, die sich in den Linecards befinden. Nachfolgend finden Sie einige Meldungen zum GSR-Puffermanagement, die in den Router-Protokollen während der Produktion angezeigt werden können. Im folgenden Abschnitt werden die verschiedenen Auslöser erläutert, die dazu führen können, dass diese Meldungen in den Routerprotokollen angezeigt werden, sowie die erforderlichen Korrekturmaßnahmen zur Behebung des Problems. In einigen Fällen kann dies auch zu Paketverlusten führen, die sich als Protokoll-Flaps manifestieren und Auswirkungen auf das Netzwerk haben können.

%EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted

SLOT 1:Sep 16 19:06:40.003 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(1) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:45.943 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(0) are available in ToFab FreeQ pool# 1

SLOT 0:Sep 16 19:06:46.267 UTC: %EE48-3-QM_SANITY_WARNING: Few free buffers(2) are available in ToFab FreeQ pool# 2

SLOT 8:Sep 16 19:06:47.455 UTC: %EE48-3-QM_SANITY_WARNING: ToFab FreeQ buffers depleted. Recarving the ToFab buffers

SLOT 8:Sep 16 19:06:47.471 UTC: %EE192-3-BM_QUIESCE:

Lösung

Hintergrund

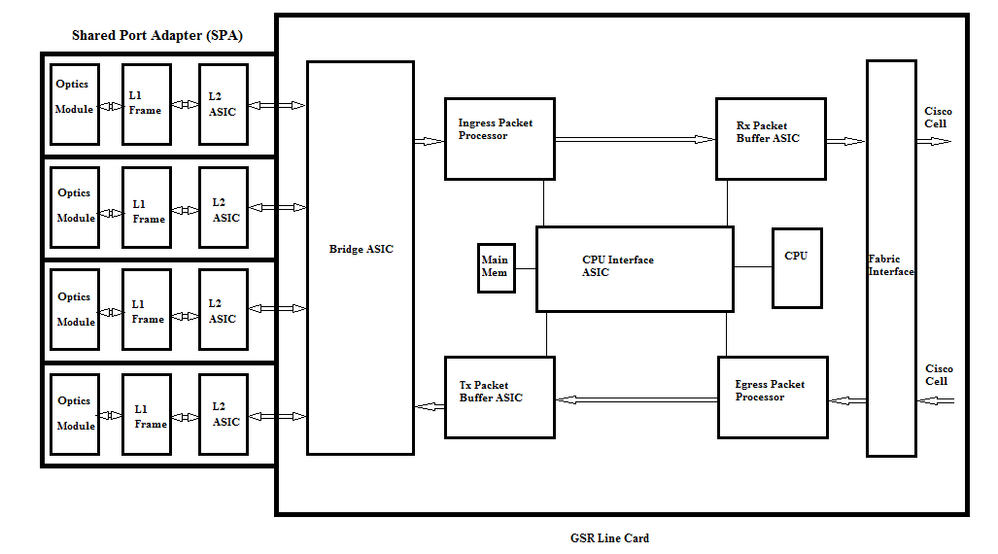

Um die QM-SANITY-Warnfehler zu beheben, müssen wir den Paketfluss auf einer GSR-Linecard verstehen. In der folgenden Abbildung werden die Hauptblöcke einer C12k-Linecard und der Paketflusspfad erläutert.

Die Linecard (LC) eines Cisco Internet Routers der Serie 12000 verfügt über zwei Speichertypen:

- Routen- oder Prozessorspeicher (Dynamic RAM - DRAM): Dieser Speicher ermöglicht in erster Linie dem integrierten Prozessor die Ausführung der Cisco IOS-Software und das Speichern von Netzwerk-Routingtabellen (Forwarding Information Base - FIB, Adjacency).

- Paketspeicher (Synchronous Dynamic RAM - SDRAM): Der Linecard-Paketspeicher speichert temporär Datenpakete, die auf eine Switching-Entscheidung durch den Linecard-Prozessor warten.

Wie aus dem obigen Bild ersichtlich, hat die GSR Line Card einen speziellen Paketpuffer ASIC( Application Specific Integrated Circuit), einer in jede Richtung des Datenflusses, der Zugriff auf den Paketspeicher bietet. Diese ASICs, die auch als Buffer Management ASIC (BMA) bekannt sind, übernehmen die Paketpuffer- und Pufferwarteschlangen-Verwaltungsfunktion auf der Line Card. Um hohe Durchsatz-/Weiterleitungsraten zu unterstützen, wird der Paketspeicher in zwei Richtungen in Speicherpools unterschiedlicher Größe unterteilt, die Pakete unterschiedlicher MTU-Größe weiterleiten.

Die von den PLIM-Karten (Physical Layer Interface Module) empfangenen Frames werden von Layer 2 verarbeitet und einem lokalen Speicher der PLIM-Karte zugewiesen. Nach Abschluss der empfangenen Dateneinheit kontaktiert ein ASIC im PLIM die Eingangs-BMA und fordert einen Puffer entsprechender Größe an. Wenn der Puffer freigegeben wird, wird das Paket in den Eingangspaketspeicher der Linecard verschoben. Wenn keine verfügbaren Puffer vorhanden sind, wird das Paket verworfen, und der ignorierte Schnittstellenzähler wird aktiviert. Der Eingangs-Paketprozessor übernimmt die Verarbeitungsfunktionen für das Paket, trifft die Weiterleitungsentscheidung und verschiebt das Paket in die Fab-Warteschlange, die der Ausgangs-Linecard entspricht. Der Fabric Interface ASIC (FIA) segmentiert das Paket in Cisco-Zellen, und die Zellen werden an die Switch-Fabric übertragen. Die Pakete werden dann von der Switch-Fabric von der FIA auf der Ausgangs-Linecard empfangen und an die Fab-Warteschlangen weitergeleitet, wo sie wieder zusammengesetzt werden. Anschließend werden sie an den Ausgangs-PLIM weitergeleitet und schließlich über die Leitung versendet.

Die Entscheidung der FrFab BMA, den Puffer aus einem bestimmten Pufferpool auszuwählen, basiert auf der Entscheidung der Eingangs-Linecard-Switching-Engine. Da alle Warteschlangen auf der gesamten Box die gleiche Größe und die gleiche Reihenfolge aufweisen, weist die Switching Engine den sendenden LC an, das Paket in die Warteschlange mit der gleichen Nummer zu stellen, von der aus es in den Router eingegeben wurde.

Während der Paketvermittlung wird die Warteschlangengröße eines bestimmten Pufferpools an der Eingangs-Linecard, mit der das Paket verschoben wurde, um eins verringert, bis die BMA in der Ausgangs-Linecard den Puffer zurückgibt. Hierbei ist zu beachten, dass das vollständige Puffermanagement in der Hardware durch die Puffermanagement-ASICs erfolgt und dass es für einen fehlerfreien Betrieb erforderlich ist, dass die BMA die Puffer an den ursprünglichen Pool zurückgibt, von dem sie bezogen wurden.

Es gibt drei Szenarien, in denen beim GSR-Paketpuffermanagement Stress oder Fehler auftreten können, die zu Paketverlusten führen. Nachfolgend sind die drei Szenarien aufgeführt.

Szenario 1:

Die Verwaltung der Hardware-Warteschlange schlägt fehl. Dies geschieht, wenn die Ausgangs-BMA den Paketpuffer nicht zurückgibt oder den Paketpuffer in einen falschen Pufferpool zurücksetzt. Wenn die Puffer an den falschen Pool zurückgegeben werden, werden einige Pufferpools wachsen, und einige Pufferpools werden über einen bestimmten Zeitraum aufgebraucht, um schließlich Pakete mit der Größe des aufgebrauchten Pufferpools zu erhalten. Die QM-Integritätswarnungen werden angezeigt, wenn der Paketpuffer den Warnungsschwellenwert überschreitet.

Verwenden Sie den Befehl QM Sanity debugs and show controller tofab queues, um zu überprüfen, ob diese Bedingung Auswirkungen auf Sie hat. Im Abschnitt zur Fehlerbehebung erfahren Sie, wie Sie QM-Integritätsschwellenwerte aktivieren.

Dieser Zustand wird in der Regel durch fehlerhafte Hardware verursacht. Überprüfen Sie die folgenden Ausgaben des Routers, und suchen Sie nach Paritätsfehlern oder Abstürzen der Linecard. Die Korrektur besteht darin, die Linecard zu ersetzen.

show controllers fia

show context all

show log

Beispiel:

Aus der QM-Sanity-Debug- und Show-Controller-tofab-Warteschlange können wir sehen, dass Pool 2 größer wird, während Pool 4 klein wird. Dies deutet darauf hin, dass Pool 4 Puffer verliert und an Pool 2 zurückgegeben wird.

QM-Sanity-Fehlersuche:

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 1: Carve Size 102001: Current Size 73078

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 2: Carve Size 78462: Current Size 181569

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 3: Carve Size 57539: Current Size 6160

SLOT 5:Oct 25 04:41:03.286 UTC: Pool 4: Carve Size 22870: Current Size 67

SLOT 5:Oct 25 04:41:03.286 UTC: IPC FreeQ: Carve Size 600: Current Size 600

Zeigt Controller-ToFab-Warteschlangen an:

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 13542 13448 73078 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 131784 131833 181569 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 184620 182591 6160 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 239113 238805 67 262143

Szenario 2:

Datenverkehrsüberlastung auf dem nächsten Hop-Gerät oder dem Weiterleitungspfad. In diesem Szenario kann das Gerät, an das der GSR Datenverkehr weiterleitet, nicht mit der Geschwindigkeit von GSR verarbeitet werden. Daher sendet das Next-Hop-Gerät Pausen-Frames an GSR, in denen es aufgefordert wird, die Geschwindigkeit zu verringern. Wenn die Flusskontrolle auf GSR PLIM-Karten aktiviert ist, berücksichtigt der Router die Pausen-Frames und beginnt mit der Pufferung der Pakete. Letztendlich gehen dem Router die Puffer aus, was zu QM-Sanity-Fehlermeldungen und Paketverlusten führt. Die QM-Integritätswarnungen werden angezeigt, wenn der Paketpuffer den Warnungsschwellenwert überschreitet. Im Abschnitt zur Fehlerbehebung erfahren Sie, wie Sie die QM-Integritätsschwellenwerte ermitteln.

Verwenden Sie die Ausgabe von show interface auf der Egress-Schnittstelle, um zu überprüfen, ob der Router von diesem Szenario betroffen ist. Die folgende Erfassung zeigt ein Beispiel für eine Schnittstelle, die Pausen-Frames empfängt. Der Aktionsplan sieht vor, die Ursachen für Überlastungen im nächsten Hop-Gerät zu untersuchen.

GigabitEthernet6/2 is up, line protocol is up

Small Factor Pluggable Optics okay

Hardware is GigMac 4 Port GigabitEthernet, address is 000b.455d.ee02 (bia 000b.455d.ee02)

Description: Cisco Sydney Lab

Internet address is 219.158.33.86/30

MTU 1500 bytes, BW 500000 Kbit, DLY 10 usec, rely 255/255, load 154/255

Encapsulation ARPA, loopback not set

Keepalive set (10 sec)

Full Duplex, 1000Mbps, link type is force-up, media type is LX

output flow-control is on, input flow-control is on

ARP type: ARPA, ARP Timeout 04:00:00

Last input 00:00:02, output 00:00:02, output hang never

Last clearing of "show interface" counters 7w1d

Queueing strategy: random early detection (WRED)

Output queue 0/40, 22713601 drops; input queue 0/75, 736369 drops

Available Bandwidth 224992 kilobits/sec

30 second input rate 309068000 bits/sec, 49414 packets/sec

30 second output rate 303400000 bits/sec, 73826 packets/sec

143009959974 packets input, 88976134206186 bytes, 0 no buffer

Received 7352 broadcasts, 0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame, 0 overrun, 0 ignored

0 watchdog, 7352 multicast, 45 pause input

234821393504 packets output, 119276570730993 bytes, 0 underruns

Transmitted 73201 broadcasts

0 output errors, 0 collisions, 0 interface resets

0 babbles, 0 late collision, 0 deferred

0 lost carrier, 0 no carrier, 0 pause output

0 output buffer failures, 0 output buffers swapped out

Szenario 3:

In Zeiten der Überbelegung aufgrund schlechten Netzwerkdesigns, Datenverkehrsspitzen und DOS-Angriffen. QM-Integritätswarnung kann auftreten, wenn ein anhaltend hoher Datenverkehrszustand vorliegt, bei dem mehr Datenverkehr auf den Router geleitet wird, als die Line Cards verarbeiten können.

Um dies zu verursachen, überprüfen Sie die Datenverkehrsraten an allen Schnittstellen im Router. Das wird zeigen, ob eine der Hochgeschwindigkeitsverbindungen langsame Verbindungen überlastet.

Verwenden Sie den Befehl show interface output.

Befehle zur Fehlerbehebung

So überprüfen Sie den aktuellen QM-Sanitätsgrad für einen LC

-

An LC anhängen

-

Zum Aktivierungsmodus wechseln

-

Test-Fab-Befehl ausführen

-

Ausgabe von "qm_sanity_info" erfassen

-

Option q zum Beenden der Test-Fab-Befehlszeile

-

Beenden von LC

So konfigurieren Sie QM-Sanitätsparameter

- Ändern des Konfigurationsmodus

- Führen Sie hw-module slot <slot#> qm-sanity tofab warning freq <> aus.

So aktivieren/deaktivieren Sie QM-Integritätsdebugs

- An LC anhängen

-

Zum Aktivierungsmodus wechseln

-

Test-Fab-Befehl ausführen

-

Führen Sie "qm_sanity_debug" aus. Führen Sie den Vorgang erneut aus, und die Fehlersuche wird beendet.

-

Option q zum Beenden der Test-Fab-Befehlszeile

-

Beenden von LC

So überprüfen Sie die grundlegenden Statistiken der GSR-Fabric-Schnittstelle

- Kontroller Fix anzeigen

So überprüfen Sie die Tofab-Warteschlangen

- Controller-ToFab-Warteschlangen anzeigen

So überprüfen Sie FRFAB-Warteschlangen

- Controller-Fab-Warteschlangen anzeigen

Beispiel:

Die folgende Ausgabe stammt von einem funktionierenden Lab-Router, um die Befehlsausgaben zu veranschaulichen.

GSR-1-PE-5#show controller fia

Fabric configuration: 10Gbps bandwidth (2.4Gbps available), redundant fabric

Master Scheduler: Slot 17 Backup Scheduler: Slot 16

Fab epoch no 0 Halt count 0

From Fabric FIA Errors

-----------------------

redund overflow 0 cell drops 0

cell parity 0

Switch cards present 0x001F Slots 16 17 18 19 20

Switch cards monitored 0x001F Slots 16 17 18 19 20

Slot: 16 17 18 19 20

Name: csc0 csc1 sfc0 sfc1 sfc2

-------- -------- -------- -------- --------

los 0 0 0 0 0

state Off Off Off Off Off

crc16 0 0 0 0 0

To Fabric FIA Errors

-----------------------

sca not pres 0 req error 0 uni fifo overflow 0

grant parity 0 multi req 0 uni fifo undrflow 0

cntrl parity 0 uni req 0

multi fifo 0 empty dst req 0 handshake error 0

cell parity 0

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_debug

QM Sanity Debug enabled

BFLC (? for help) [qm_sanity_debug]:

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

SLOT 1:02:54:33: ToFAB BMA information

SLOT 1:02:54:33: Number of FreeQs carved 4

SLOT 1:02:54:33: Pool 1: Carve Size 102001: Current Size 102001

SLOT 1:02:54:33: Pool 2: Carve Size 78462: Current Size 78462

SLOT 1:02:54:33: Pool 3: Carve Size 57539: Current Size 57539

SLOT 1:02:54:33: Pool 4: Carve Size 22870: Current Size 22870

SLOT 1:02:54:33: IPC FreeQ: Carve Size 600: Current Size 600

SLOT 1:02:54:33: Number of LOQs enabled 768

SLOT 1:02:54:33: Number of LOQs disabled 1280

QM Sanity Debug disabled

BFLC (? for help) [qm_sanity_debug]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 20 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exi

Disconnecting from slot 1.

Connection Duration: 00:01:09

GSR-1-PE-5#config t

Enter configuration commands, one per line. End with CNTL/Z.

GSR-1-PE-5(config)#hw-module slot 1 qm-sanity tofab warning freq 10

GSR-1-PE-5(config)#end

GSR-1-PE-5#attach 1

02:57:25: %SYS-5-CONFIG_I: Configured from console by console

GSR-1-PE-5#attach 1

Entering Console for Modular SPA Interface Card in Slot: 1

Type "exit" to end this session

Press RETURN to get started!

LC-Slot1>en

LC-Slot1#test fab

BFLC diagnostic console program

BFLC (? for help) [?]: qm_sanity_info

ToFab QM Sanity level Warning

FrFab QM Sanity level None

Sanity Check is triggered every 10 seconds

Min. buffers threshold in percentage 5

BFLC (? for help) [qm_sanity_info]: q

LC-Slot1#exit

Disconnecting from slot 1.

Connection Duration: 00:00:27

GSR-1-PE-5#execute-on all show controllers tofab queues

========= Line Card (Slot 0) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262141/262141 buffers specified/carved

265028848/265028848 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

107232/107232 (buffers specified/carved), 40.90%, 80 byte data size

601 107832 107232 262143

73232/73232 (buffers specified/carved), 27.93%, 608 byte data size

107833 181064 73232 262143

57539/57539 (buffers specified/carved), 21.94%, 1616 byte data size

181065 238603 57539 262143

23538/23538 (buffers specified/carved), 8.97%, 4592 byte data size

238604 262141 23538 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

155 154 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

15 2191(hpr) 0 0 0 0

Multicast 2048 0 0 0 262143

2049 0 0 0 262143

========= Line Card (Slot 1) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: 26000000, carve base: 26010000

268369920 bytes carve size, 4 SDRAM bank(s), 32768 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

262140/261472 buffers specified/carved

267790176/264701344 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

102001/102001 (buffers specified/carved), 39.1%, 80 byte data size

1 601 102601 102001 262143

78462/78462 (buffers specified/carved), 30.0%, 608 byte data size

2 102602 181063 78462 262143

57539/57539 (buffers specified/carved), 22.0%, 1616 byte data size

3 181064 238602 57539 262143

23538/22870 (buffers specified/carved), 8.74%, 4592 byte data size

4 238603 261472 22870 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

30 85 84 600 262143

Raw Queue (high priority):

27 0 0 0 65368

Raw Queue (medium priority):

28 0 0 0 32684

Raw Queue (low priority):

31 0 0 0 16342

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

=============================================================

::::::::::::::::::::

Hi Priority

0 2176(hpr) 0 0 0

1 2177(hpr) 0 0 0

2 2178(hpr) 0 0 0

3 2179(hpr) 0 0 0

4 2180(hpr) 553 552 0

5 2181(hpr) 0 0 0

6 2182(hpr) 0 0 0

7 2183(hpr) 0 0 0

8 2184(hpr) 0 0 0

9 2185(hpr) 0 0 0

10 2186(hpr) 0 0 0

11 2187(hpr) 0 0 0

12 2188(hpr) 0 0 0

13 2189(hpr) 0 0 0

14 2190(hpr) 0 0 0

15 2191(hpr) 0 0 0

Multicast

2048 0 0 0

2049 0 0 0

2050 0 0 0

2051 0 0 0

2052 0 0 0

2053 0 0 0

2054 0 0 0

2055 0 0 0

========= Line Card (Slot 3) =========

Carve information for ToFab buffers

SDRAM size: 268435456 bytes, address: E0000000, carve base: E0018000

268337152 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4112 bytes, min buffer data size 80 bytes

262142/262142 buffers specified/carved

230886224/230886224 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

3 non-IPC free queues:

94155/94155 (buffers specified/carved), 35.91%, 80 byte data size

601 94755 94155 262143

57539/57539 (buffers specified/carved), 21.94%, 608 byte data size

94756 152294 57539 262143

109848/109848 (buffers specified/carved), 41.90%, 1616 byte data size

152295 262142 109848 262143

IPC Queue:

600/600 (buffers specified/carved), 0.22%, 4112 byte data size

207 206 600 262143

Raw Queue (high priority):

0 0 0 65535

Raw Queue (medium priority):

0 0 0 32767

Raw Queue (low priority):

0 0 0 16383

ToFab Queues:

Dest Slot Queue# Head Tail Length Threshold

pkts pkts

==============================================================

0 0 0 0 0 262143

1 0 0 0 262143

2 0 0 0 262143

3 0 0 0 262143

:::::::::::::::::::::::::::

2049 0 0 0 262143

2050 0 0 0 262143

2051 0 0 0 262143

2052 0 0 0 262143

2053 0 0 0 262143

2054 0 0 0 262143

2055 0 0 0 262143

GSR-1-PE-5#execute-on slot 2 show controller frfab queues

========= Line Card (Slot 2) =========

Carve information for FrFab buffers

SDRAM size: 268435456 bytes, address: D0000000, carve base: D241D100

230567680 bytes carve size, 4 SDRAM bank(s), 16384 bytes SDRAM pagesize, 2 carve(s)

max buffer data size 4592 bytes, min buffer data size 80 bytes

235926/235926 buffers specified/carved

226853664/226853664 bytes sum buffer sizes specified/carved

Qnum Head Tail #Qelem LenThresh

---- ---- ---- ------ ---------

4 non-IPC free queues:

96484/96484 (buffers specified/carved), 40.89%, 80 byte data size

11598 11597 96484 262143

77658/77658 (buffers specified/carved), 32.91%, 608 byte data size

103116 103115 77658 262143

40005/40005 (buffers specified/carved), 16.95%, 1616 byte data size

178588 178587 40005 262143

21179/21179 (buffers specified/carved), 8.97%, 4592 byte data size

214748 235926 21179 262143

IPC Queue:

600/600 (buffers specified/carved), 0.25%, 4112 byte data size

66 65 600 262143

Multicast Raw Queue:

0 0 0 58981

Multicast Replication Free Queue:

235930 262143 26214 262143

Raw Queue (high priority):

78 77 0 235927

Raw Queue (medium priority):

11596 11595 0 58981

Raw Queue (low priority):

0 0 0 23592

Interface Queues:

Interface Queue# Head Tail Length Threshold

pkts pkts

======================================================

0 0 103107 103106 0 32768

3 178588 178587 0 32768

1 4 103110 103109 0 32768

7 11586 11585 0 32768

2 8 0 0 0 32768

11 0 0 0 32768

3 12 0 0 0 32768

15 0 0 0 32768

GSR-1-PE-5#

Revisionsverlauf

| Überarbeitung | Veröffentlichungsdatum | Kommentare |

|---|---|---|

1.0 |

30-Jul-2017 |

Erstveröffentlichung |

Beiträge von Cisco Ingenieuren

- Shabeer MansoorCisco TAC

Cisco kontaktieren

- Eine Supportanfrage öffnen

- (Erfordert einen Cisco Servicevertrag)

Feedback

Feedback